# Effective downsampling techniques for SEM defect inspection using design insights in machine learning

Qian Xie, S Keerthibala Viswanatha, Srividya Jayaram, Sudheesh Krishnankutty, Frederic Huguennet, Rakesh Soni, Aparna Basu

SIEMENS EDA, Digital Industries Software

Qian Xie| SEMI Advanced Semiconductor Manufacturing Conference, May 2024 | © Siemens 2024 |Siemens Digital Industries Software

### Outline

- Introduction

- Methodology

- Experiments and Results

- Process Window Qualification

- ROI (Return-Of-Investment)

- Conclusion

SIEMENS

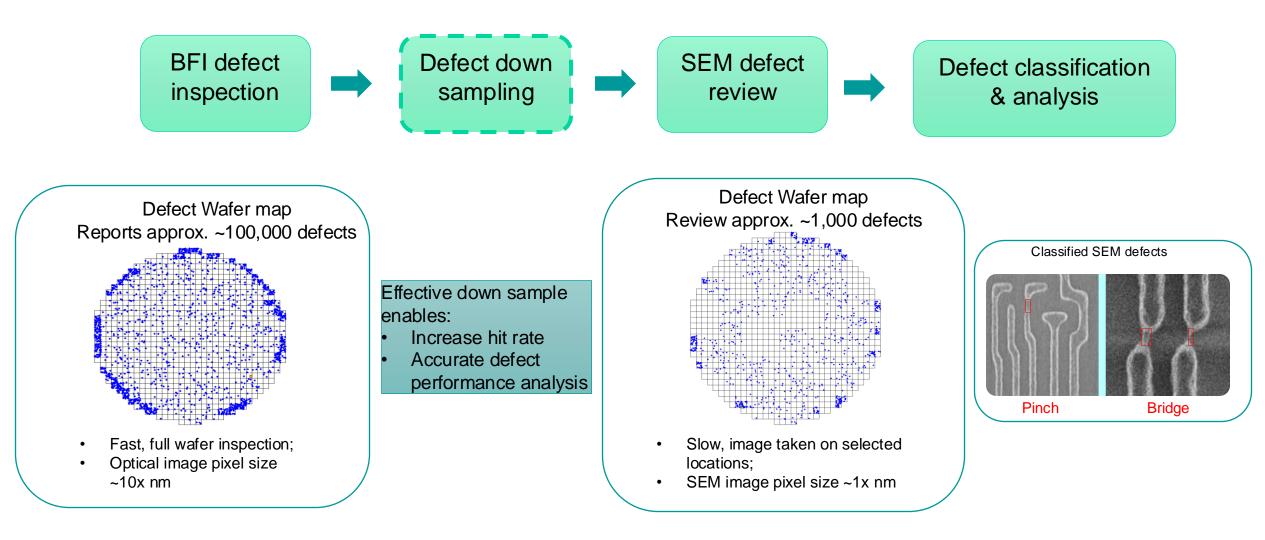

#### Introduction to wafer defect down sampling flow

#### **Methodology**

#### -- Defect down sample with design and process information

- Design systematics in wafer manufacturing:

- Design systematics are often seen in R&D stage of new tech node development

- Process and design systematics can happen during yield ramp up even HVM, especially on wafer edge dies

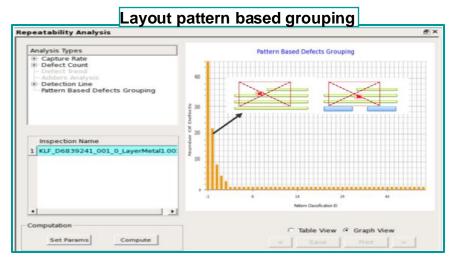

- Defect down sampling in Calibre Wafer Defect Management (GUI based):

- Layout pattern based: perform pattern-based defect grouping, sample as many pattern variety as possible

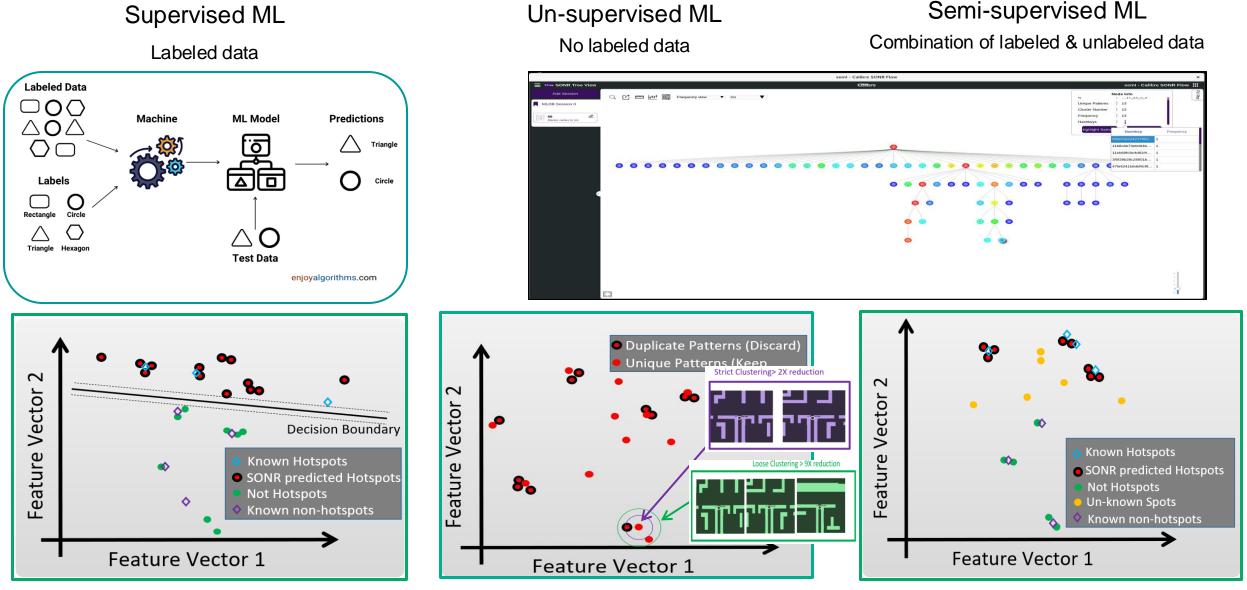

- Machine learning based (integrating Calibre SONR): with features not limited to layout geometry, but various design/process/defect signal features, sample based on selected feature group similarity

Qian Xie| SEMI Advanced Semiconductor Manufacturing Conference, May 2024 | © Siemens 2024 | Siemens Digital Industries Software

#### Machine learning methods in Calibre SONR

Qian Xie| SEMI Advanced Semiconductor Manufacturing Conference, May 2024 | © Siemens 2024 | Siemens Digital Industries Software

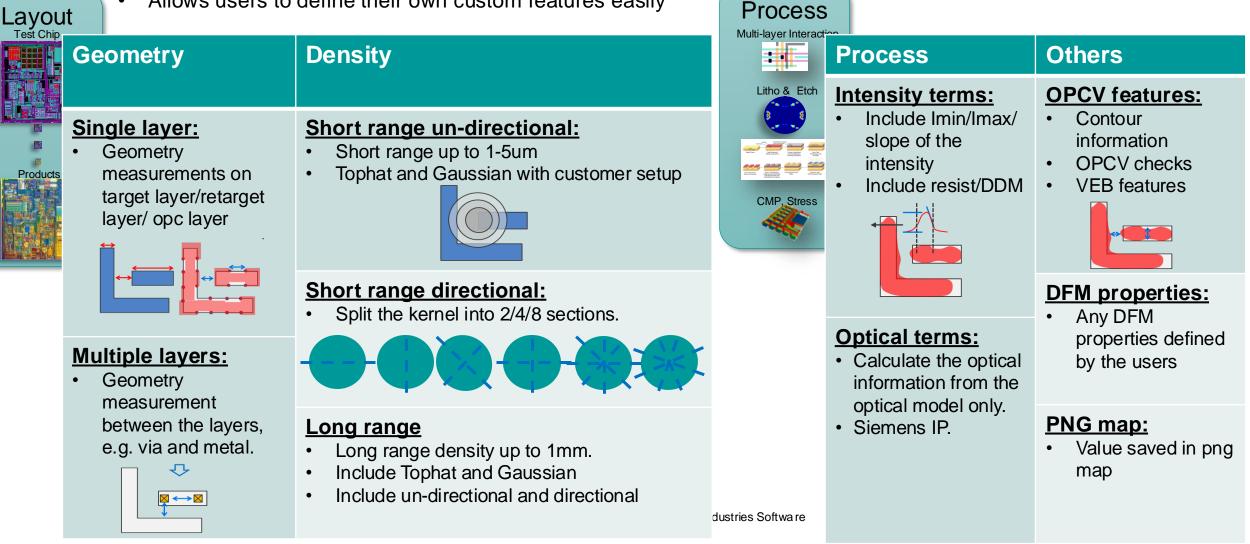

#### **Calibre SONR feature engineering**

- Feature Engineering is one of the most critical tasks in success with ML applications.

- Internal SONR features include layout and process information

- · Allows users to define their own custom features easily

#### **Experiments and Results**

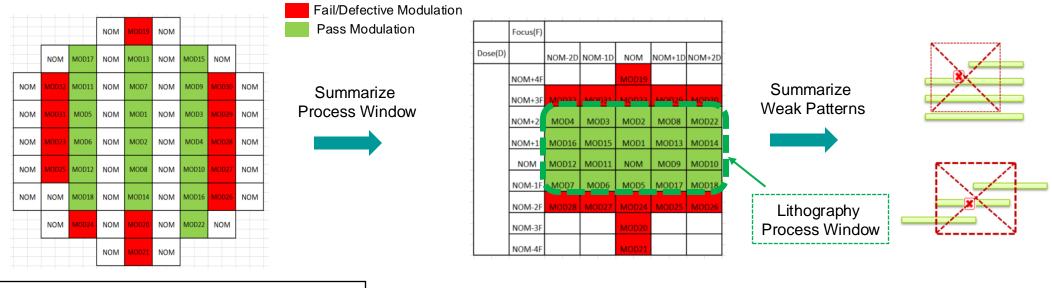

Process Window Qualification

SIFMENS

Lithography print wafer with different exposure/focus

Customer A: using both Pattern based + ML down sampling vs fab POR Customer B: using only ML down sampling vs fab POR

#### **Benchmark results**

#### Customer A<sup>[1]</sup>

| PWQ analysis<br>Dataset 1        | Baseline | Pattern based<br>+ Machine Leaning |

|----------------------------------|----------|------------------------------------|

| Defect Hit Rate                  | 1x       | 2x                                 |

| # of Systematic<br>Weak Patterns | 1x       | 4x                                 |

| # of Failing Process<br>Windows  | 1x       | 1.25x                              |

| PWQ analysis<br>Dataset 2        | Baseline | Pattern based<br>+ Machine Leaning |

|----------------------------------|----------|------------------------------------|

| Defect Hit Rate                  | 1x       | 36x*                               |

| # of Systematic<br>Weak Patterns | 1x       | 57x*                               |

| # of Failing Process<br>Windows  | 1x       | 2x                                 |

Customer B<sup>[2]</sup>

| PWQ analysis                     | Baseline | Machine Learning |

|----------------------------------|----------|------------------|

| Defect Hit Rate                  | 1x       | 40x              |

| # of Systematic<br>Weak Patterns | 1x       | 6х               |

| # of Failing Process<br>Windows  | 1x       | 1.5x             |

[1] J. Jiang et al., "Reducing Systematic Defects using Calibre Wafer Defect Engineering and Machine Learning Solutions," 2020 International Workshop on Advanced Patterning Solutions (IWAPS)

[2] Y.Ma, J Optiz et al, "Cross produces hotspot detection with Calibre SONR: A machine learning technique" 2020, DAC conference

\*note that dataset 2 has large improvements as the POR method sampled a large number of nuisance defects of same pattern

Qian Xie| SEMI Advanced Semiconductor Manufacturing Conference, May 2024 | © Siemens 2024 | Siemens Digital Industries Software

#### SIEMENS

#### **ROI (Return-Of-Investment)**

| Proposed method                                                                                                               | ROI Calculation                                                                                                       |                                                                                                             |  |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| technical benefits                                                                                                            | Volume production                                                                                                     | R&D Development                                                                                             |  |

| Higher SEM defect hit rate with<br>lower SEM review defect count<br>Customer POR: 1x<br>Proposed method:2x                    |                                                                                                                       |                                                                                                             |  |

| Discovery more weak patterns<br>with less rounds of SEM<br>review/defect inspection<br>Customer POR: 1x<br>Proposed method:4x | Expedite volume production of customers with multiple products (common IP→solve 1 product, benefits many);            | Expedite development cycle by reducing mask re-spin rounds which save significant amount of money and time; |  |

|                                                                                                                               | Reduce yield loss by reducing design systematics which makes each wafer more profitable;<br>Reduce reliability issues | Decrease yield ramp up time                                                                                 |  |

SIEMENS

#### Conclusion

- Proposed pattern based + machine learning based defect down sampling flow

- Experiments shows the proposed flow provides :

- Increased defect hit rate

- More accurate lithography process window

- More systematic pattern varieties found

- Return-Of-Investment analysis shows proposed method benefits in:

- Tool and engineer time saving

- Mask re-spin reduction and yield improvements

- Yield ramp up acceleration and reliability issue reduction

## Thank you!

Contact: <u>qian.xie@siemens.com</u>

Qian Xie| SEMI Advanced Semiconductor Manufacturing Conference, May 2024 | © Siemens 2024 | Siemens Digital Industries Software