### SIEMENS EDA

# How to Print Cell Hierarchy Path with Calibre DESIGNrev Scripting

2023.4

Page 1 © Siemens 2024 | Siemens Digital Industries Software | Where today meets tomorrow.

This package includes SVRF/TVF Technology owned by Siemens Industries Software Inc. or its affiliates (collectively, "SISW"). "SVRF/TVF Technology" means SISW's proprietary Standard Verification Rule Format ("SVRF") and Tcl Verification Format ("TVF") languages for expressing process rules. SVRF/TVF Technology constitutes or contains trade secrets and confidential information of SISW and any use is subject to the terms of SISW's standard End User License Agreement together with the Electronic Design Automation (EDA) Supplemental Terms.

SVRF/TVF Technology may be used solely with SISW EDA Software products, by your company's employees and on-site contractors, excluding EDA Competitors, who are under obligations of confidentiality and whose job performance requires access for your internal business purposes. For purposes of this paragraph, "EDA Competitor" means any individual or entity that is in the business of developing, marketing, or providing electronic design automation solutions including but not limited to applications software, intellectual property, and embedded products, or associated consulting and support services.

## Outline

- Objective

- Included Files

- Description

- Directions

- Conclusion

### **Objective**

This Support kit offers printing the cell hierarchy path and its bbox information, using a Calibre DESIGNrev Tcl script.

| File                  | Description                                                 |

|-----------------------|-------------------------------------------------------------|

| layout.gds            | Sample GDS file                                             |

| layout.gds.layerprops | Layer properties file                                       |

| cell_list.txt         | Text file includes a list of cell names                     |

| script.tcl            | Tcl script to return the cell hierarchy path in a text file |

| runme                 | Script to Calibre DESIGNrev with Tcl code                   |

## **Description**

- Calibre DESIGNrev provides a convenient way to return reference cell information by using the command \$L iterator ref. The returned information is in the following format: {cell\_name x y mirror angle mag [{properties}]} path {bbox}}

- \$L iterator ref takes 4 required arguments specifying the *cell name* that contains the objects to be returned and the *range* of elements to return with indices *startRange* through *endRange*

- The command also has multiple optional arguments such as:

- -depth startDepth endDepth: specifying the hierarchical output of objects between startDepth and endDepth with the search beginning in the specified cell (the required cell name option).

- -filterCell list\_of\_cells: used to return only objects that reference the specified list\_of\_cells.

# Description >> Tcl Script

• The Tcl script is invoked by a Calibre DESIGNrev batch run as such:

calibredrv script.tcl <layout\_name> <cell\_list.txt>

- It takes two required arguments for the input:

- **layout\_name:** the first argument is the layout file name

- **cell\_list.txt:** the second argument is the text file that contains specified cell names

- The script generates an output text file "cell\_list.txt\_out.txt". That file contains the following:

- The total instance reference count for the specified cell

- The possible hierarchical path for each reported instance

- The origin of each reported instance

- the bbox information for each reported instance

Note:

• The bbox (bounding box) information are as follows: The first two values are the lower left corner coordinates, and the last two values are the upper right corner coordinates of the bounding box

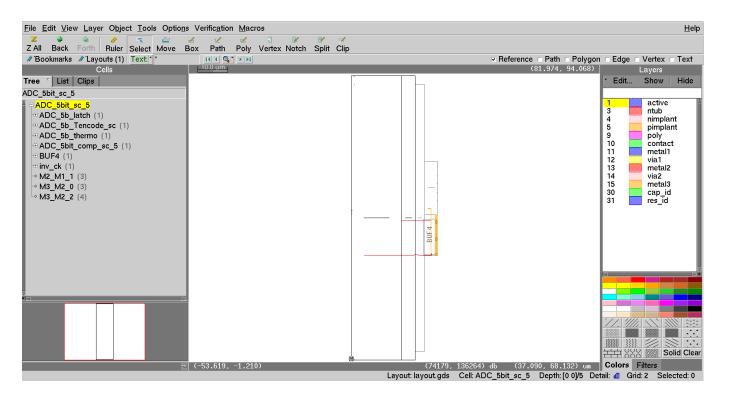

# Description >> Layout.gds

• View the sample layout with the command

calibredrv layout.gds

• To view all the hierarchy, press 9

# Description >> Layout.gds

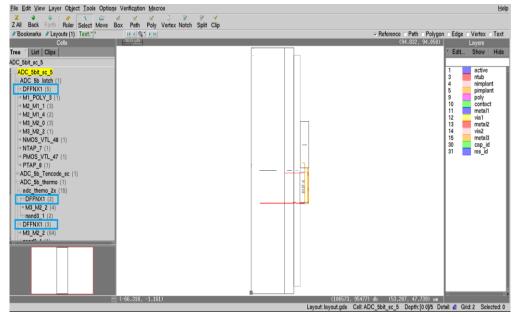

- In the cells tree, expand the following cells:

- "ADC\_5b\_latch"

- "ADC\_5b\_thermo"

- "adc\_themo\_2x"

- You can observe that cell "DFFNX1" is referenced 38 times in the layout file.

- In the cells tree, expand the following cell:

- ADC\_5b\_Tencode\_sc

- You can observe that cell "ADC\_5b\_Tencode\_sc\_frame\_x2\_ug" is referenced 3 times in the layout file.

| le Edit View Layer Object Iools Options Verification Macros |                                                               |                        |     |

|-------------------------------------------------------------|---------------------------------------------------------------|------------------------|-----|

| Z 🛊 🍖 🥒 🧮 🚔 🖉 X Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z         | V V<br>Dit Clip                                               |                        |     |

| Bookmarks / Layouts (1) Text * H ( Q * )                    | ✓ Reference ⊂ Path ⊂ Polygon ⊂                                | Edge Vertex            | Te  |

| Cells 10.0 um                                               | (94.832, 94.058)                                              | Layers                 | iii |

| ee T List Clips                                             |                                                               |                        | Н   |

| IC_5bit_sc_5                                                |                                                               |                        | _   |

| ADC_5bit_sc_5                                               |                                                               | active                 | _   |

| • ADC_5b_latch (1)                                          |                                                               | 8 ntub                 |     |

| ADC_5b_Tencode_sc (1)                                       |                                                               |                        |     |

| ADC_5b_Tencode_sc_frame (1)                                 |                                                               |                        | n.  |

| ADC_5b_Tencode_sc_frame_x2 (12)                             |                                                               | 0 contact              |     |

| ADC_5b_Tencode_sc_frame_x2_ug (3)                           |                                                               | 1 metal1<br>2 via1     |     |

| M1_POLY_3 (62)                                              |                                                               | 3 metal2               |     |

| ◇ M2_M1_4 (191)                                             |                                                               | 4 via2                 |     |

| → M3_M2_2 (157)                                             |                                                               | 5 metal3<br>30 cap_id  |     |

| NMOS_VTL_0 (13)                                             |                                                               | 80 cap_id<br>81 res_id |     |

| NMOS_VTL_12 (6)                                             |                                                               |                        |     |

| ◇ NMOS_VTL_13 (7)                                           |                                                               |                        |     |

| NMOS_VTL_2 (4)                                              |                                                               |                        |     |

| NMOS_VTL_4 (26)                                             |                                                               |                        |     |

| NMOS_VTL_5 (37)                                             |                                                               |                        |     |

| → NMOS_VTL_6 (12) → PMOS_VTL_1 (3)                          |                                                               |                        |     |

| PMOS_VTL_10 (4)                                             |                                                               |                        |     |

|                                                             |                                                               |                        |     |

| PMOS_VTL_14 (1)                                             |                                                               |                        |     |

| DUOS VITL 2 (10)                                            |                                                               |                        |     |

|                                                             |                                                               |                        |     |

|                                                             |                                                               |                        |     |

|                                                             |                                                               |                        |     |

|                                                             |                                                               |                        |     |

|                                                             |                                                               |                        |     |

| - (-66.318, -1.161)                                         | **                                                            |                        | =   |

| (-66.318, -1.161)                                           | Layout: layout.gds Cell: ADC_5bit_sc_5 Depth: [0 0]/5 Detail: |                        |     |

• Please close Calibre DESIGNrev after examining the layout file

# Description >> runme

The runme file executes one Calibre DESIGNrev run followed by an execution of a Tcl script at invocation

#!/bin/csh

calibredrv script.tcl layout.gds cell\_list.txt

- The **cell\_list.txt** file lists the cells whose paths are required to be reported

- For this test case, the cells DFFNX1 and ADC\_5b\_Tencode\_sc\_frame\_x2\_ug are specified

DFFNX1 ADC\_5b\_Tencode\_sc\_frame\_x2\_ug

Note:

Clear any empty lines in the "cell\_list.txt file" to avoid any run error

• To execute the **runme** file, write the following in the opened terminal:

#### source runme

- This run generates the output text file "cell\_list.xt\_out.txt". it contains the cell instances information as mentioned in the transcript

- # Cell instance info is written to file cell\_list.txt\_out.txt

- You can open the generated text file "cell\_list.txt\_out.txt" using any text editor tool

### **Directions**

#### The output text file "cell\_list.txt\_out.txt"

Cell =DFFNX1 Count =38 Path 1 = ADC 5bit sc 5/ADC 5b latch (X,Y) = (24.25,56.4) $bbox = \{ 24.25 \}$ 56.025 27.725 59.595 Path 2 = ADC 5bit sc 5/ADC 5b latch (X,Y) = (24.25,50.76)bbox = { 24.25 50.385 27.725 53.955 Path 3 = ADC\_5bit\_sc\_5/ADC\_5b\_latch (X, Y) = (24.25, 62.04)bbox = { 24.25 61.665 27.725 65.235 Path 4 = ADC 5bit sc 5/ADC 5b latch (X,Y) = (24.25,56.4)bbox = { 24.25 53.205 27.725 56.775 Path 5 = ADC 5bit sc 5/ADC 5b latch (X,Y) = (24.25,62.04)bbox = { 24.25 27.725 62.415 58.845 Path 6 = ADC 5bit sc 5/ADC 5b thermo (X,Y) = (16.70500000000002,0.0)bbox = { 16.70500000000002 -0.375 20.18 3.195000000000003 } Path 7 = ADC 5bit sc 5/ADC 5b thermo (X,Y) = (16.70500000000002,90.24) $bbox = \{ 16.70500000000002 \ 89.865 \ 20.18 \ 93.435 \}$ (X,Y) = (16.70500000000002,90.24)Path 8 = ADC 5bit sc 5/ADC 5b thermo bbox = { 16.70500000000002 87.045 20.18 90.615 Path 9 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,73.3200000000001) bbox = { 16.70500000000002 72.94500000000001 20.18 76.515 Path 10 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,73.3200000000001)bbox = { 16.70500000000002 70.125 20.18 73.6950000000001 Path 11 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x bbox = { 16,70500000000002 78,5850000000001 20,18 82,155 Path 12 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x bbox = { 16.70500000000002 75.765 20.18 79.3350000000001 Path 13 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002.62.04)bbox = { 16,70500000000002 61,665 20.18 65.235  $bbox = \{ 16.705000000000002 \}$ Path 14 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,62.04)58.845 20.18 62.415 Path 15 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,67.68) bbox = { 16.70500000000002 67.305 20.18 70.875 Path 16 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,67.68)bbox = { 16.70500000000002 64.485 20.18 68.055 Path 17 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,50.76) bbox = { 16.70500000000002 50.385 20.18 53.955 Path 18 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,50.76)bbox = { 16.70500000000002 47.565 20.18 51.135 Path 19 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,56.4)bbox = { 16.70500000000002 56.025 20.18 59.595 Path 20 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X, Y) = (16.70500000000002, 56.4)bbox = { 16.70500000000002 53.205 20.18 56.775 Path 21 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,45.12)bbox = { 16.705000000000002 44.745 20.18 48.315 } Path 22 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X, Y) = (16.70500000000002, 45.12) $bbox = \{ 16.70500000000002 \ 41.9250000000004 \ 20.18 \ 45.495 \} \}$ Path 23 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.705000000000002,39.48000000000000) bbox = { 16.70500000000002 39.1050000000004 20.18 42.675000000000004} (X,Y) = (16.705000000000002,39.480000000000000) Path 24 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x bbox = { 16.70500000000002 36.2850000000004 20.18 39.855000000000004 } Path 25 = ADC\_5bit\_sc\_5/ADC\_5b\_thermo/adc\_themo\_2x (X,Y) = (16.70500000000002,28.2)bbox = { 16.70500000000002 27.825 20.18 31.395 } Path 26 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,28.2) $bbox = {$ 16.70500000000002 25.005 20.18 28.575 } Path 27 = ADC\_5bit\_sc\_5/ADC\_5b\_thermo/adc\_themo\_2x (X,Y) = (16.70500000000002,33.84)bbox = { 16.70500000000002 33.465 20.18 37.03500000000004 } Path 28 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002.33.84)bbox = { 16,70500000000002 30,645 20,18 34.215 } Path 29 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002, 16.92)bbox = { 16.70500000000002 16.545 20.18 20.11500000000002 } Path 30 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,16.92) bbox = { 16.70500000000000 13.725 20.18 17.295 bbox = { 16.70500000000002 22.185 20.18 25.755 Path 31 = ADC\_5bit\_sc\_5/ADC\_5b\_thermo/adc\_themo\_2x (X,Y) = (16.70500000000002,22.56) Path 32 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,22.56) bbox = { 16.70500000000002 19.3650000000002 20.18 22.935 } Path 33 = ADC 5bit\_sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,11.28) bbox = { 16.705000000000002 10.905 20.18 14.475 } Path 34 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16,705000000000002,11,28) $bbox = \{ 16.70500000000002 8.085 20.18 11.655 \}$ Path 35 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x(X,Y) = (16.70500000000002,5.64)bbox = { 16.70500000000002 5.265 20.18 8.835 } Path 36 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,5.64)bbox = { 16.70500000000002 2.445 20.18 6.01500000000001 } Path 37 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,84.600000000001) bbox = { 16.70500000000002 84.2250000000001 20.18 87.795 Path 38 = ADC 5bit sc 5/ADC 5b thermo/adc themo 2x (X,Y) = (16.70500000000002,84.600000000001) bbox = { 16.70500000000002 81.405 20.18 84.97500000000001 Cell =ADC\_5b\_Tencode\_sc\_frame\_x2\_ug Count =3 Path 1 = ADC 5bit sc 5/ADC 5b Tencode sc (X,Y) = (21.0425.36.66000000000000) $bbox = \{ 21.0425 \ 36.28 \ 24.25 \ 42.68 \}$ Path 2 = ADC 5bit sc 5/ADC 5b Tencode sc (X, Y) = (21.0425, 31.02)bbox = { 21.0425 30.64 24.25 37.04 }  $bbox = \{ 21.0425 \ 41.92 \ 24.25 \ 48.32 \}$ Path 3 = ADC 5bit sc 5/ADC 5b Tencode sc (X,Y) = (21,0425,42,30000000000000)

#### 38 instances of cell "DFFNX1"

3 instances of cell "ADC\_5b\_Tencode\_sc\_frame\_x2\_ug"

#### Note:

All dimensions are in microns

SIEMENS

- Dealing with full-chip layouts requires a quick access to cell instances information such as the instance path or the bounding box information

- **\$L iterator ref** is a very powerful Calibre DESIGNrev command, with vast optional arguments, that returns a list of the specified type of references with several information about each reference such as instance path, coordinates of the cell origin, angle of rotation, mirroring information, geometrical properties and bbox information

Please refer to the Calibre® DESIGNrev<sup>™</sup> Reference Manual for additional information

Unpublished work. © 2024 Siemens

This software or file (the "Material") contains trade secrets or otherwise confidential information owned by Siemens Industry Software Inc. or its affiliates (collectively, "SISW"), or SISW's licensors. Access to and use of this information is strictly limited as set forth in one or more applicable agreement(s) with SISW. This material may not be copied, distributed, or otherwise disclosed without the express written permission of SISW, and may not be used in any way not expressly authorized by SISW.

Unless otherwise agreed in writing, SISW has no obligation to support or otherwise maintain this Material. No representation or other affirmation of fact herein shall be deemed to be a warranty or give rise to any liability of SISW whatsoever.

SISW reserves the right to make changes in specifications and other information contained herein without prior notice, and the reader should, in all cases, consult SISW to determine whether any changes have been made.

SISW MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF INTELLECTUAL PROPERTY. SISW SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, CONSEQUENTIAL OR PUNITIVE DAMAGES, LOST DATA OR PROFITS, EVEN IF SUCH DAMAGES WERE FORESEEABLE, ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF SISW HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

TRADEMARKS: The trademarks, logos, and service marks (collectively, "Marks") used herein are the property of Siemens AG, SISW, or their affiliates (collectively, "Siemens") or other parties. No one is permitted to use these Marks without the prior written consent of Siemens or the owner of the Marks, as applicable. The use herein of third party Marks is not an attempt to indicate Siemens as a source of a product, but is intended to indicate a product from, or associated with, a particular third party. A list of Siemens' Marks may be viewed at: <a href="http://www.plm.automation.siemens.com/global/en/legal/trademarks.html">http://www.plm.automation.siemens.com/global/en/legal/trademarks.html</a>

Support Center: <u>https://support.sw.siemens.com/</u> Send Feedback on Documentation: <u>https://support.sw.siemens.com/doc\_feedback\_form</u>